5 V mixer/oscillator and synthesizer for PAL and NTSC standards

Rev. 02 — 14 June 2005

Product data sheet

### 1. General description

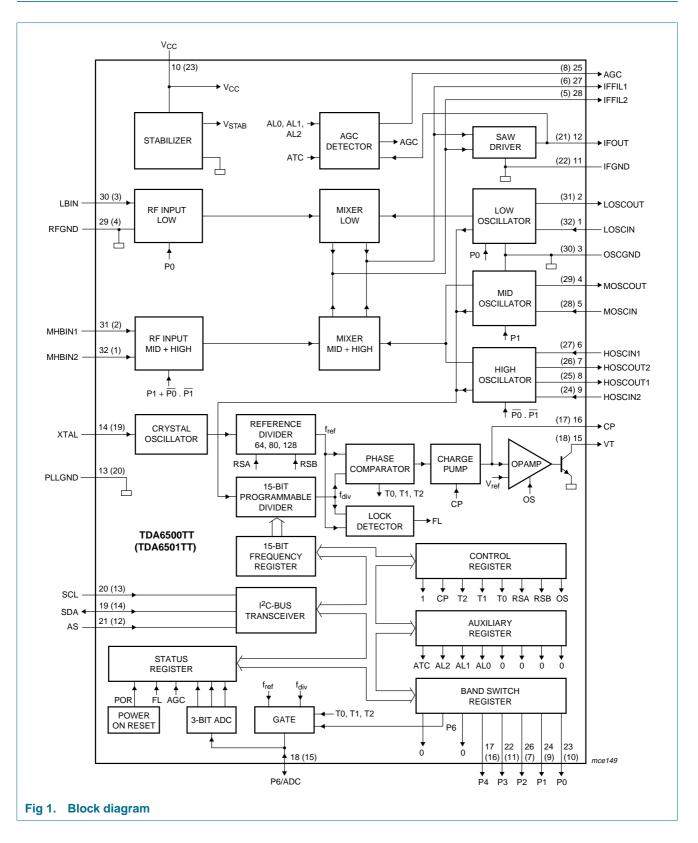

TDA6500TT and TDA6501TT are programmable 2-mixer, 3-oscillator and synthesizer MOPLLs intended for pure 3-band tuner concepts.

The device includes two double balanced mixers for the low and mid/high bands and three oscillators for the low, mid and high bands, respectively. Other functions are an IF amplifier, a wide-band AGC detector and a PLL synthesizer. Two pins are available between the mixer output and the IF amplifier input to enable IF filtering for improved signal handling.

The device can be controlled according to the I<sup>2</sup>C-bus format.

### 2. Features

- Single-chip, 5 V mixer/oscillator and synthesizer for TV and VCR tuners

- I<sup>2</sup>C-bus protocol compatible with 3.3 V and 5 V microcontrollers:

- Address + 6 data bytes transmission

- Address + 1 status byte (I<sup>2</sup>C-bus read mode)

- Four independent I<sup>2</sup>C-bus addresses

- Two PMOS open-drain ports with 5 mA source capability to switch high band and FM sound trap (P2 and P3)

- One PMOS open-drain port P1 with 20 mA source capability to switch the mid band

- One PMOS open-drain port P0 with 10 mA source capability to switch the low band

- Five step, 3-bit Analog-to-Digital Converter (ADC) and NPN open-collector general purpose port P6 with 5 mA sinking capability

- NPN open-collector general purpose port P4 with 5 mA sinking capability

- Internal AGC flag

- In-lock flag

- 33 V tuning voltage output

- 15-bit programmable divider

- Programmable reference divider ratio: 64, 80 or 128

- Programmable charge pump current: 60 μA or 280 μA

- Varicap drive disable

- Balanced mixer with a common emitter input for the low band (single input)

- Balanced mixer with a common base input for the mid and high bands (balanced input)

- 2-pin asymmetrical oscillator for the low band

- 2-pin asymmetrical oscillator for the mid band

- 4-pin symmetrical oscillator for the high band

# PHILIPS

# **TDA6500; TDA6501**

### 5 V mixer/oscillator and synthesizer for PAL and NTSC standards

- IF preamplifier with asymmetrical 75 Ω output impedance to drive a SAW filter (500 Ω/40 pF)

- Wide-band AGC detector for internal tuner AGC:

- Five programmable take-over points

- Two programmable time constants

# 3. Applications

- TV and VCR tuners

- Specially suited for switched concepts, all systems

- Specially suited for strong off-air reception

### 4. Ordering information

#### Table 1:Ordering information

| Type number | Package | Package                                              |          |  |  |  |  |  |

|-------------|---------|------------------------------------------------------|----------|--|--|--|--|--|

|             | Name    | Description                                          | Version  |  |  |  |  |  |

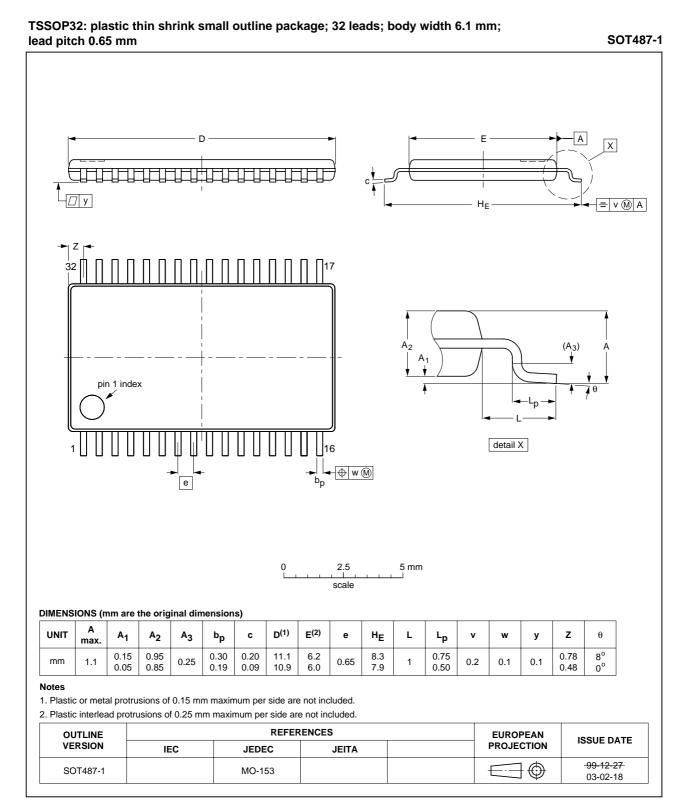

| TDA6500TT   | TSSOP32 | plastic thin shrink small outline package; 32 leads; | SOT487-1 |  |  |  |  |  |

| TDA6501TT   |         | body width 6.1 mm; lead pitch 0.65 mm                |          |  |  |  |  |  |

5 V mixer/oscillator and synthesizer for PAL and NTSC standards

# 5. Block diagram

5 V mixer/oscillator and synthesizer for PAL and NTSC standards

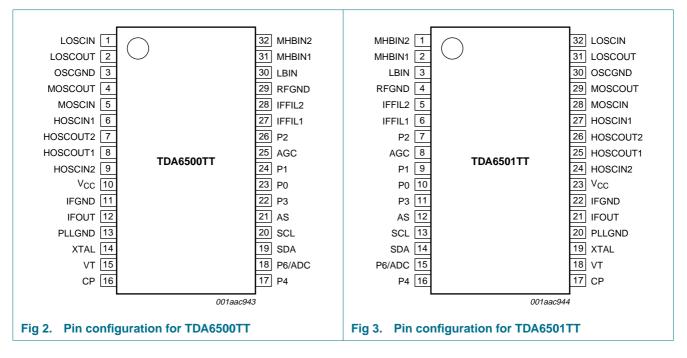

# 6. Pinning information

### 6.1 Pinning

### 6.2 Pin description

#### Table 2: Pin description

| Symbol   | Pin       |           | Description                   |  |  |  |  |

|----------|-----------|-----------|-------------------------------|--|--|--|--|

|          | TDA6500TT | TDA6501TT |                               |  |  |  |  |

| AGC      | 25        | 8         | AGC output                    |  |  |  |  |

| AS       | 21        | 12        | address selection input       |  |  |  |  |

| СР       | 16        | 17        | charge pump output            |  |  |  |  |

| HOSCIN1  | 6         | 27        | high band oscillator input 1  |  |  |  |  |

| HOSCIN2  | 9         | 24        | high band oscillator input 2  |  |  |  |  |

| HOSCOUT1 | 8         | 25        | high band oscillator output 1 |  |  |  |  |

| HOSCOUT2 | 7         | 26        | high band oscillator output 2 |  |  |  |  |

| IFFIL1   | 27        | 6         | IF filter output 1            |  |  |  |  |

| IFFIL2   | 28        | 5         | IF filter output 2            |  |  |  |  |

| IFGND    | 11        | 22        | IF ground                     |  |  |  |  |

| IFOUT    | 12        | 21        | IF output                     |  |  |  |  |

| LBIN     | 30        | 3         | low band RF input             |  |  |  |  |

| LOSCIN   | 1         | 32        | low band oscillator input     |  |  |  |  |

| LOSCOUT  | 2         | 31        | low band oscillator output    |  |  |  |  |

| MHBIN1   | 31        | 2         | mid and high band RF input 1  |  |  |  |  |

| MHBIN2   | 32        | 1         | mid and high band RF input 2  |  |  |  |  |

| MOSCIN   | 5         | 28        | mid band oscillator input     |  |  |  |  |

### 5 V mixer/oscillator and synthesizer for PAL and NTSC standards

| Symbol          | Pin                |    | Description                                            |

|-----------------|--------------------|----|--------------------------------------------------------|

|                 | TDA6500TT TDA6501T |    |                                                        |

| MOSCOUT         | 4                  | 29 | mid band oscillator output                             |

| OSCGND          | 3                  | 30 | oscillator ground                                      |

| P0              | 23                 | 10 | PMOS open-drain port 0 to select low band operation    |

| P1              | 24                 | 9  | PMOS open-drain port 1 to select mid band operation    |

| P2              | 26                 | 7  | PMOS open-drain general purpose port 2                 |

| P3              | 22                 | 11 | PMOS open-drain general purpose port 3                 |

| P4              | 17                 | 16 | NPN open-collector general purpose port 4              |

| P6/ADC          | 18                 | 15 | NPN open-collector general purpose port 6 or ADC input |

| PLLGND          | 13                 | 20 | digital ground                                         |

| RFGND           | 29                 | 4  | RF ground                                              |

| SCL             | 20                 | 13 | serial clock input                                     |

| SDA             | 19                 | 14 | serial data input and output                           |

| V <sub>CC</sub> | 10                 | 23 | supply voltage                                         |

| VT              | 15                 | 18 | tuning voltage output                                  |

| XTAL            | 14                 | 19 | crystal oscillator input                               |

### 7. Functional description

### 7.1 General

TDA6500TT and TDA6501TT are programmable 2-mixer, 3-oscillator and synthesizer MOPLLs intended for pure 3-band tuner concepts.

The device includes two double balanced mixers for the low and mid/high bands and three oscillators for the low, mid and high bands respectively. The band limits for PAL tuners are shown in Table 3.

#### Table 3:Low, mid and high band limits

| Band | Input f <sub>RFpix</sub> (MHz) |        | Oscillator f <sub>osc</sub> (MHz) |        |  |  |

|------|--------------------------------|--------|-----------------------------------|--------|--|--|

|      | Min                            | Мах    | Min                               | Max    |  |  |

| Low  | 45.25                          | 154.25 | 84.15                             | 193.15 |  |  |

| Mid  | 161.25                         | 439.25 | 200.15                            | 478.15 |  |  |

| High | 455.25                         | 855.25 | 494.15                            | 894.15 |  |  |

Other functions are an IF amplifier, a wide-band AGC detector and a PLL synthesizer.

Two pins are available between the mixer output and the IF amplifier input to enable IF filtering for improved signal handling.

Bit P0 enables Port P0 and the low band mixer and oscillator (see <u>Table 4</u>). Bit P1 enables Port P1, the mid/high band mixer and the mid band oscillator. Bit P2 enables Port P2 and bit P3 enables Port P3. When Ports P0 and P1 are disabled, the mid/high band mixer and the high band oscillator are enabled.

| Table 4. | Mixer and Oscillator band selection |          |     |      |         |                 |      |  |  |  |

|----------|-------------------------------------|----------|-----|------|---------|-----------------|------|--|--|--|

| Bit      |                                     | Mixer ba | and |      | Oscilla | Oscillator band |      |  |  |  |

| P0       | P1                                  | low      | mid | high | low     | mid             | high |  |  |  |

| 1        | 0                                   | x        |     |      | x       |                 |      |  |  |  |

| 0        | 1                                   |          | х   | х    |         | х               |      |  |  |  |

| 0        | 0                                   |          | х   | х    |         |                 | х    |  |  |  |

#### Table 4: Mixer and oscillator band selection

The AGC detector provides information about the IF amplifier level. Five AGC take-over points are available by software. Two programmable AGC time constants are available for search tuning and normal tuner operation. The synthesizer consists of a 15-bit programmable divider, a crystal oscillator and its programmable reference divider and a phase/frequency detector combined with a charge pump, which drives the tuning amplifier including 33 V output.

Depending on the reference divider ratio (64, 80 or 128) the phase comparator operates at 62.50 kHz, 50.00 kHz or 31.25 kHz with a 4 MHz crystal.

The device can be controlled according to the  $I^2$ C-bus format. The lock detector bit FL is set to logic 1 when the loop is locked. The AGC bit is set to logic 1 when the internal AGC is active (level below 3 V). These two flags are read on the SDA line (status byte) during a read operation (see Table 11).

The ADC input is available on pin P6/ADC for digital AFC control. The ADC code is read during a read operation (see <u>Table 11</u>). In test mode, pin P6/ADC is used as a test output for  $\frac{1}{2}f_{ref}$  and  $\frac{1}{2}f_{div}$  (see <u>Table 8</u>).

A minimum of seven bytes, including address byte, is required to address the device, select the VCO frequency, program the ports, set the charge pump current, set the reference divider ratio, select the AGC take-over point and select the AGC time constant. The device has four independent l<sup>2</sup>C-bus addresses which can be selected by applying a specific voltage on input AS (see Table 7).

### 7.2 Device control

The device is controlled via the  $I^2C$ -bus. For programming, a module address of 7 bits and the R/ $\overline{W}$  bit for selecting the read or the write mode is required.

### 7.2.1 Write mode

Data bytes can be sent to the device after the address transmission (first byte). Seven data bytes are needed to fully program the device. The bus transceiver has an auto-increment facility, which permits the programming of the device within one single transmission (address + 6 data bytes).

The device can also be partially programmed providing that the first data byte following the address is the first divider byte DB1 or the control byte CB. The data bytes are defined in Table 5 and Table 6.

The first bit of the first data byte indicates whether frequency data (first bit = 0) or control, port and auxiliary data (first bit = 1) will follow. Until an  $I^2C$ -bus STOP command is sent by the controller, additional data bytes can be entered without the need to re-address the device. The frequency register is loaded with data from byte DB2 after the 8th SCL clock

pulse, the control register is loaded with data from byte CB after the 8th SCL clock pulse, the band switch register is loaded with data of byte BB after the 8th SCL clock pulse and the auxiliary register is loaded with data of byte AB after the 8th SCL clock pulse.

To program the AGC take-over point setting and the AGC current to a different value than the default value, an additional byte, the auxiliary byte, has to be sent. To this end, the auxiliary byte is preceded by a control byte with the test bits T2, T1 and T0 set to logic 011 (see Table 8).

### Table 5: I<sup>2</sup>C-bus data format for write mode

| Name                          | Byte | Bit |     |     |     |     |     |     | Ack                  |   |

|-------------------------------|------|-----|-----|-----|-----|-----|-----|-----|----------------------|---|

|                               |      | MSB |     |     |     |     |     |     | LSB                  |   |

| Address byte                  | ADB  | 1   | 1   | 0   | 0   | 0   | MA1 | MA0 | $R/\overline{W} = 0$ | А |

| Divider byte 1                | DB1  | 0   | N14 | N13 | N12 | N11 | N10 | N9  | N8                   | А |

| Divider byte 2                | DB2  | N7  | N6  | N5  | N4  | N3  | N2  | N1  | N0                   | А |

| Control byte                  | СВ   | 1   | СР  | T2  | T1  | Т0  | RSA | RSB | OS                   | А |

| Band switch byte              | BB   | 0   | P6  | 0   | P4  | P3  | P2  | P1  | P0                   | А |

| Auxiliary byte <sup>[1]</sup> | AB   | ATC | AL2 | AL1 | AL0 | 0   | 0   | 0   | 0                    | А |

[1] Auxiliary byte AB replaces band switch byte BB when bit T2 = 0, T1 = 1 and T0 = 1.

| Symbol           | Description                                                                                                                                |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| A                | acknowledge                                                                                                                                |  |  |  |  |  |

| MA1 and MA0      | programmable address bits; see Table 7                                                                                                     |  |  |  |  |  |

| R/W              | logic 0 for write mode                                                                                                                     |  |  |  |  |  |

| N14 to N0        | programmable divider bits;<br>N = (N14 $\times$ 2 <sup>14</sup> ) + (N13 $\times$ 2 <sup>13</sup> ) + + (N1 $\times$ 2 <sup>1</sup> ) + N0 |  |  |  |  |  |

| СР               | charge pump current                                                                                                                        |  |  |  |  |  |

|                  | $CP = 0$ : the charge pump current is 60 $\mu A$                                                                                           |  |  |  |  |  |

|                  | CP = 1: the charge pump current is 280 $\mu$ A (default)                                                                                   |  |  |  |  |  |

| T2, T1 and T0    | test bits; see Table 8                                                                                                                     |  |  |  |  |  |

| RSA and RSB      | reference divider ratio select bits; see Table 9                                                                                           |  |  |  |  |  |

| OS               | tuning amplifier control bit                                                                                                               |  |  |  |  |  |

|                  | OS = 0: normal operation; tuning voltage is on                                                                                             |  |  |  |  |  |

|                  | OS = 1: tuning voltage is off; high-impedance state (default)                                                                              |  |  |  |  |  |

| P6 and P4        | NPN port control bits                                                                                                                      |  |  |  |  |  |

|                  | Pn = 0: port n is off; high-impedance state (default)                                                                                      |  |  |  |  |  |

|                  | $Pn = 1$ : buffer n is on; $V_O = V_{CE(sat)}$                                                                                             |  |  |  |  |  |

| P3 to P0         | PMOS port control bits                                                                                                                     |  |  |  |  |  |

|                  | Pn = 0: port n is off; high-impedance state (default)                                                                                      |  |  |  |  |  |

|                  | Pn = 1: buffer n is on; $V_O = V_{CC} - V_{DS(sat)}$                                                                                       |  |  |  |  |  |

| ATC              | AGC time constant                                                                                                                          |  |  |  |  |  |

|                  | ATC = 0: $I_{AGC}$ = 220 nA; $\Delta t$ = 2 s with C = 160 nF (default)                                                                    |  |  |  |  |  |

|                  | ATC = 1: $I_{AGC}$ = 9 $\mu$ A; $\Delta t$ = 50 ms with C = 160 nF                                                                         |  |  |  |  |  |

| AL2, AL1 and AL0 | AGC take-over point bits; see Table 10                                                                                                     |  |  |  |  |  |

|                  |                                                                                                                                            |  |  |  |  |  |

#### Table 6: Description of bits shown in Table 5

7 of 37

### 5 V mixer/oscillator and synthesizer for PAL and NTSC standards

The module address contains programmable address bits (MA1 and MA0) which offer the possibility of having up to 4 synthesizers in one system by applying a specific voltage on the AS input. <u>Table 7</u> gives the relationship between the input voltage applied to the AS input and bits MA1 and MA0.

#### Table 7: I<sup>2</sup>C-bus address selection

| Voltage applied to pin AS                | MA1 | MA0 |

|------------------------------------------|-----|-----|

| 0 V to 0.1V <sub>CC</sub>                | 0   | 0   |

| $0.2V_{CC}$ to $0.3V_{CC}$ or open       | 0   | 1   |

| 0.4V <sub>CC</sub> to 0.6V <sub>CC</sub> | 1   | 0   |

| 0.9V <sub>CC</sub> to V <sub>CC</sub>    | 1   | 1   |

#### Table 8: Test modes

| T2 | T1 | Т0 | Test modes                                                                       |  |  |  |  |  |

|----|----|----|----------------------------------------------------------------------------------|--|--|--|--|--|

| 0  | 0  | 0  | normal mode                                                                      |  |  |  |  |  |

| 0  | 0  | 1  | normal mode; default mode at power-on reset                                      |  |  |  |  |  |

| 0  | 1  | 0  | charge pump is off                                                               |  |  |  |  |  |

| 0  | 1  | 1  | control byte is followed by auxiliary byte AB instead of the band switch byte BB |  |  |  |  |  |

| 1  | 1  | 0  | charge pump is sinking current                                                   |  |  |  |  |  |

| 1  | 1  | 1  | charge pump is sourcing current                                                  |  |  |  |  |  |

| 1  | 0  | 0  | <sup>1</sup> / <sub>2</sub> f <sub>ref</sub> is available on pin P6/ADC [1]      |  |  |  |  |  |

| 1  | 0  | 1  | <sup>1</sup> / <sub>2</sub> f <sub>div</sub> is available on pin P6/ADC [1]      |  |  |  |  |  |

|    |    |    |                                                                                  |  |  |  |  |  |

[1] The ADC input cannot be used when these test modes are active; see Section 7.2.2 for more information.

### Table 9: Reference divider ratio select

| RSA | RSB | Reference divider ratio |

|-----|-----|-------------------------|

| 0   | 0   | 80                      |

| 0   | 1   | 128                     |

| 1   | 1   | 64                      |

| 1   | 0   | forbidden               |

### Table 10: AGC take-over point

| AL2 | AL1 | AL0 | Asymmetrical mode                              |  |  |  |

|-----|-----|-----|------------------------------------------------|--|--|--|

| 0   | 0   | 0   | 115 dBµV                                       |  |  |  |

| 0   | 0   | 1   | 115 dBµV                                       |  |  |  |

| 0   | 1   | 0   | 112 dB $\mu$ V; default mode at power-on reset |  |  |  |

| 0   | 1   | 1   | 109 dBµV                                       |  |  |  |

| 1   | 0   | 0   | 106 dBµV                                       |  |  |  |

| 1   | 0   | 1   | 103 dBµV                                       |  |  |  |

| 1   | 1   | 0   | I <sub>AGC</sub> = 0 mA; external AGC [1]      |  |  |  |

| 1   | 1   | 1   | 3.5 V; disabled [1]                            |  |  |  |

|     |     |     |                                                |  |  |  |

[1] The AGC detector is disabled. Both the sinking and sourcing currents from the IC are disabled. The AGC output goes into a high-impedance state and an external AGC source can be connected in parallel.

[2] The AGC detector is disabled and the fast mode current source is enabled.

### 7.2.2 Read mode

Data can be read from the device by setting the  $R/\overline{W}$  bit to logic 1. The data read format is shown in <u>Table 11</u>. After the slave address has been recognized, the device generates an acknowledge pulse and the first data byte (status byte) is transferred on the SDA line with the MSB first. Data is valid on the SDA line during a HIGH-level of the SCL clock signal.

A second data byte can be read from the device if the microcontroller generates an acknowledge on the SDA line (master acknowledge). End of transmission will occur if no master acknowledge occurs. The device will then release the data line to allow the microcontroller to generate a STOP condition.

The POR flag is set to logic 1 at power-on. The flag is reset when an end-of-data is detected by the device (end of a read sequence).

Control of the loop is made possible with the in-lock flag (FL) which indicates when the loop is locked (FL = 1).

The internal AGC status is available from the AGC bit. AGC = 1 indicates when the selected take-over point is reached.

A built-in ADC is available on the P6/ADC pin. The ADC can be used to apply AFC information to the microcontroller from the IF section of the tuner. The relationship between the voltage applied to the ADC input and the A2, A1 and A0 bits is given in Table 13.

### Table 11: Read data format

| Name         | Byte | Bit                | Bit |   |   |     |     |     |         |   |  |

|--------------|------|--------------------|-----|---|---|-----|-----|-----|---------|---|--|

|              |      | MSB <sup>[1]</sup> |     |   |   |     |     |     | LSB     |   |  |

| Address byte | ADB  | 1                  | 1   | 0 | 0 | 0   | MA1 | MA0 | R/W = 1 | А |  |

| Status byte  | SB   | POR                | FL  | 1 | 1 | AGC | A2  | A1  | A0      | - |  |

[1] MSB is transmitted first.

#### Table 12: Description of bits shown in Table 11

| Symbol        | Description                                      |

|---------------|--------------------------------------------------|

| A             | acknowledge                                      |

| MA1 and MA0   | programmable address bits; see Table 7           |

| R/W           | logic 1 for read mode                            |

| POR           | power-on reset flag                              |

|               | POR = 0, normal operation                        |

|               | POR = 1, power-on state                          |

| FL            | in-lock flag                                     |

|               | FL = 0, not locked                               |

|               | FL = 1, the PLL is locked                        |

| AGC           | internal AGC flag                                |

|               | AGC = 0, internal AGC not active                 |

|               | AGC = 1, internal AGC is active; level below 3 V |

| A2, A1 and A0 | digital output of the 5-level ADC; see Table 13  |

| Table 13: ADC levels             |    |    |    |

|----------------------------------|----|----|----|

| Voltage applied to ADC input [1] | A2 | A1 | A0 |

| $0.60V_{CC}$ to $V_{CC}$         | 1  | 0  | 0  |

| $0.45V_{CC}$ to $0.60V_{CC}$     | 0  | 1  | 1  |

| $0.30V_{CC}$ to $0.45V_{CC}$     | 0  | 1  | 0  |

| $0.15V_{CC}$ to $0.30V_{CC}$     | 0  | 0  | 1  |

| 0 V to 0.15V <sub>CC</sub>       | 0  | 0  | 0  |

[1] Accuracy is  $\pm 0.03 V_{CC}$ .

### 7.2.3 Power-on reset

The power-on detection threshold voltage is set to  $V_{POR} = 3.5$  V at room temperature. Below this threshold, the device is reset to the power-on state.

In the power-on state, the charge pump current is set to  $280 \ \mu$ A, the tuning voltage output is disabled, the test bits T2 = 0, T1 = 0 and T0 = 1, the AGC take-over point is set to 112 dB $\mu$ V and the AGC current is set to the slow mode. The high band is selected by default.

#### Table 14: Default bits at power-on reset

| Name             | Byte | Bit |   |   |   |   |     |     |     |

|------------------|------|-----|---|---|---|---|-----|-----|-----|

|                  |      | MSB |   |   |   |   |     |     | LSB |

| Address byte     | ADB  | 1   | 1 | 0 | 0 | 0 | MA1 | MA0 | Х   |

| Divider byte 1   | DB1  | 0   | Х | Х | Х | Х | Х   | Х   | Х   |

| Divider byte 2   | DB2  | Х   | Х | Х | Х | Х | Х   | Х   | Х   |

| Control byte     | СВ   | 1   | 1 | 0 | 0 | 1 | Х   | Х   | 1   |

| Band switch byte | BB   | -   | 0 | - | 0 | 0 | 0   | 0   | 0   |

| Auxiliary byte   | AB   | 0   | 0 | 1 | 0 | - | -   | -   | -   |

5 V mixer/oscillator and synthesizer for PAL and NTSC standards

# 8. Internal circuitry

| Table 15: In<br>Symbol | ternal circuits<br>Pin |           | Average D | C voltage ve | rsus band | Equivalent circuit <sup>[1]</sup>                  |

|------------------------|------------------------|-----------|-----------|--------------|-----------|----------------------------------------------------|

|                        |                        |           | selection |              |           |                                                    |

|                        | TDA6500TT              | TDA6501TT | Low       | Mid          | High      |                                                    |

| LOSCIN                 | 1                      | 32        | 1.7       | 1.4          | 1.4       |                                                    |

| LOSCOUT                | 2                      | 31        | 2.9       | 3.5          | 3.5       | (32) 1 - Ce222                                     |

| OSCGND                 | 3                      | 30        | -         | -            | -         | -                                                  |

| MOSCOUT                | 4                      | 29        | 3.5       | 3.02         | 3.5       |                                                    |

| MOSCIN                 | 5                      | 28        | 1.4       | 1.7          | 1.4       | (28) 5                                             |

| HOSCIN1                | 6                      | 27        | 2.2       | 2.2          | 1.8       |                                                    |

| HOSCOUT2               | 7                      | 26        | 5         | 5            | 2.5       |                                                    |

| HOSCOUT1               | 8                      | 25        | 5         | 5            | 2.5       | Ц Ц <sub>–</sub>                                   |

| HOSCIN2                | 9                      | 24        | 2.2       | 2.2          | 1.8       | (25) 8 7 (2<br>(27) 6 9 (2<br>(27) 6 <i>mce141</i> |

| V <sub>CC</sub>        | 10                     | 23        | 5.0       | 5.0          | 5.0       | -                                                  |

| IFGND                  | 11                     | 22        | -         | -            | -         | 11 (22)<br><i>tce225</i>                           |

| IFOUT                  | 12                     | 21        | 2.1       | 2.1          | 2.1       | 12 (21)<br>fce226                                  |

### 9397 750 15057

# **TDA6500; TDA6501**

### 5 V mixer/oscillator and synthesizer for PAL and NTSC standards

| Symbol | Pin       |           | Average D<br>selection            | C voltage ve                      | ersus band                        | Equivalent circuit [1]                                                  |

|--------|-----------|-----------|-----------------------------------|-----------------------------------|-----------------------------------|-------------------------------------------------------------------------|

|        | TDA6500TT | TDA6501TT | Low                               | Mid                               | High                              | _                                                                       |

| PLLGND | 13        | 20        | -                                 | -                                 | -                                 | 13 (20)<br>fce227                                                       |

| XTAL   | 14        | 19        | 0.7                               | 0.7                               | 0.7                               | 14 (19)<br>mce142                                                       |

| VT     | 15        | 18        | V <sub>VT</sub>                   | V <sub>VT</sub>                   | V <sub>VT</sub>                   | 15 (18)<br>mce143                                                       |

| СР     | 16        | 17        | 1.0                               | 1.0                               | 1.0                               |                                                                         |

| P4     | 17        | 16        | V <sub>CE(sat)</sub><br>or High Z | V <sub>CE(sat)</sub><br>or High Z | V <sub>CE(sat)</sub><br>or High Z | 17 (16)<br>mce145                                                       |

| P6/ADC | 18        | 15        | V <sub>CE(sat)</sub><br>or High Z | V <sub>CE(sat)</sub><br>or High Z | V <sub>CE(sat)</sub><br>or High Z | (15) 18 (15) 18 (15) 18 (15) 18 (15) (15) (15) (15) (15) (15) (15) (15) |

### Table 15: Internal circuits ...continued

# **TDA6500; TDA6501**

### 5 V mixer/oscillator and synthesizer for PAL and NTSC standards

| Symbol | Pin       |           | Average DC selection              | C voltage ver                                  | sus band                                       | Equivalent circuit [1]                   |

|--------|-----------|-----------|-----------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------|

|        | TDA6500TT | TDA6501TT | Low                               | Mid                                            | High                                           |                                          |

| SDA    | 19        | 14        | n.a.                              | n.a.                                           | n.a.                                           | (14) 19                                  |

| SCL    | 20        | 13        | n.a.                              | n.a.                                           | n.a.                                           | (13) 20                                  |

| AS     | 21        | 12        | 1.25                              | 1.25                                           | 1.25                                           | (12) 21 (12) 21 (12) 21 (12) (12) (12) ( |

| P3     | 22        | 11        |                                   | High Z or<br>V <sub>CC</sub> – V <sub>DS</sub> | High Z or<br>V <sub>CC</sub> – V <sub>DS</sub> | 22 (11)<br>fce236                        |

| P0     | 23        | 10        | V <sub>CC</sub> – V <sub>DS</sub> | High Z                                         | High Z                                         | 23 (10)<br>fce237                        |

| P1     | 24        | 9         |                                   | V <sub>CC</sub> – V <sub>DS</sub>              |                                                | 24 (9)<br>fce238                         |

| AGC    | 25        | 8         | 0 V or 3.5 V                      | 0 V or 3.5 V                                   | 0 V or 3.5 V                                   | 25 (8)<br>fce239                         |

### Table 15: Internal circuits ...continued

9397 750 15057 Product data sheet

# **TDA6500; TDA6501**

### 5 V mixer/oscillator and synthesizer for PAL and NTSC standards

| Symbol | Pin       |           | Average DO selection                           | C voltage ver                                  | sus band                                       | Equivalent circuit [1]  |

|--------|-----------|-----------|------------------------------------------------|------------------------------------------------|------------------------------------------------|-------------------------|

|        | TDA6500TT | TDA6501TT | Low                                            | Mid                                            | High                                           |                         |

| P2     | 26        | 7         | High Z or<br>V <sub>CC</sub> – V <sub>DS</sub> | High Z or<br>V <sub>CC</sub> – V <sub>DS</sub> | High Z or<br>V <sub>CC</sub> – V <sub>DS</sub> | 26 (7)<br>fce240        |

| IFFIL1 | 27        | 6         | 4.4                                            | 4.4                                            | 4.4                                            |                         |

| IFFIL2 | 28        | 5         | 4.4                                            | 4.4                                            | 4.4                                            |                         |

| RFGND  | 29        | 4         | -                                              | -                                              | -                                              | 29 (4)                  |

| LBIN   | 30        | 3         | 1.8                                            | n.a.                                           | n.a.                                           | (3) 30                  |

| MHBIN1 | 31        | 2         | n.a.                                           | 1.0                                            | 1.0                                            |                         |

| MHBIN2 | 32        | 1         | n.a.                                           | 1.0                                            | 1.0                                            | (2) 31 32 (1)<br>mce148 |

#### Table 15: Internal circuits ...continued

[1] The pin numbers in parenthesis represent the TDA6501TT.

5 V mixer/oscillator and synthesizer for PAL and NTSC standards

# 9. Limiting values

| Symbol                            | Parameter                                | Conditions | Min  | Max                   | Unit |

|-----------------------------------|------------------------------------------|------------|------|-----------------------|------|

| V <sub>CC</sub>                   | supply voltage                           |            | -0.3 | +6                    | V    |

| V <sub>XTAL</sub>                 | crystal input voltage                    |            | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| V <sub>P6/ADC</sub>               | NPN port input and output voltage        |            | -0.3 | V <sub>CC</sub> + 0.3 | V    |

| I <sub>P6/ADC</sub>               | NPN port output current (open-collector) |            | 0    | 10                    | mA   |

| V <sub>VT</sub>                   | tuning voltage output                    |            | -0.3 | +35                   | V    |

| V <sub>CP</sub>                   | charge pump output voltage               |            | -0.3 | $V_{CC} + 0.3$        | V    |

| V <sub>P4</sub>                   | NPN port output voltage (open-collector) |            | -0.3 | $V_{CC} + 0.3$        | V    |

| I <sub>P4</sub>                   | NPN port output current (open-collector) |            | 0    | 10                    | mA   |

| V <sub>SDA</sub>                  | serial data input/output voltage         |            | -0.3 | +6                    | V    |

| I <sub>SDA</sub>                  | serial data output current               |            | -1   | +10                   | mA   |

| V <sub>SCL</sub>                  | serial clock input voltage               |            | -0.3 | +6                    | V    |

| V <sub>AS</sub>                   | address selection input voltage          |            | -0.3 | $V_{CC} + 0.3$        | V    |

| V <sub>Pn</sub>                   | PMOS port output voltage (open-drain)    |            | -0.3 | $V_{CC} + 0.3$        | V    |

| I <sub>P1</sub>                   | PMOS port output current (open-drain)    |            | -25  | 0                     | mA   |

| I <sub>P0</sub>                   | PMOS port output current (open-drain)    |            | -15  | 0                     | mA   |

| I <sub>P2</sub> , I <sub>P3</sub> | PMOS port output current (open-drain)    |            | -10  | 0                     | mA   |

| T <sub>stg</sub>                  | storage temperature                      |            | -40  | +150                  | °C   |

| T <sub>amb</sub>                  | ambient temperature                      |            | -20  | +85                   | °C   |

| Tj                                | junction temperature                     |            | -    | 150                   | °C   |

[1] Maximum ratings cannot be exceeded, not even momentarily without causing irreversible IC damage. Maximum ratings cannot be accumulated.

# **10. Thermal characteristics**

| Table 17:            | Thermal characteristics                     |                                                                     |                    |      |

|----------------------|---------------------------------------------|---------------------------------------------------------------------|--------------------|------|

| Symbol               | Parameter                                   | Conditions                                                          | Тур                | Unit |

| SOT487E              | C3 package (TDA6500TT)                      |                                                                     |                    |      |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air; one layer<br>printed-circuit board,<br>JEDEC standards | [ <u>1]</u> 110    | K/W  |

| SOT487E              | C5 package (TDA6501TT)                      |                                                                     |                    |      |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air; one layer<br>printed-circuit board,<br>JEDEC standards | <sup>[1]</sup> 115 | K/W  |

[1] The thermal resistance is highly dependant on the printed-circuit board on which the package is mounted. The thermal resistance values are given only for customer's guidance.

# **11. Characteristics**

#### Table 18: Supplies

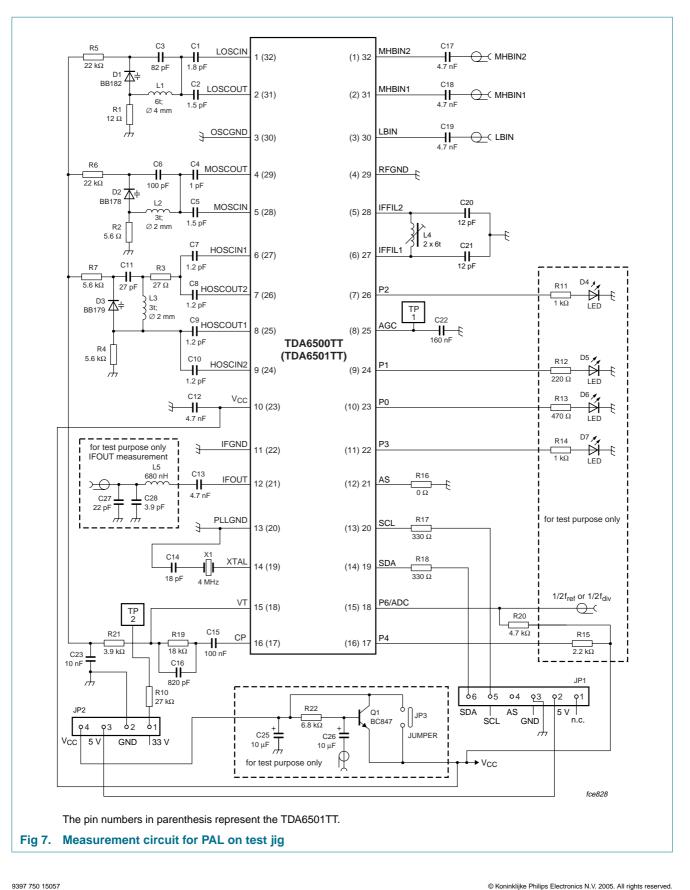

$V_{CC} = 5 V$ ;  $T_{amb} = 25 \circ C$ ; values are given for an IF amplifier with 500  $\Omega$  load (measured as shown in Figure 7 for the PAL standard); unless otherwise specified.

| Symbol          | Parameter      | Conditions                                                              | Min | Тур | Max | Unit |

|-----------------|----------------|-------------------------------------------------------------------------|-----|-----|-----|------|

| Supply          |                |                                                                         |     |     |     |      |

| V <sub>CC</sub> | supply voltage |                                                                         | 4.5 | 5.0 | 5.5 | V    |

| I <sub>CC</sub> | supply current | all PNP ports off                                                       | -   | 74  | 94  | mA   |

|                 |                | one PNP port on; sourcing 20 mA                                         | -   | 96  | 116 | mA   |

|                 |                | two PNP ports on; one port sourcing 20 mA; one other port sourcing 5 mA |     | 102 | 122 | mA   |

#### Table 19: PLL

$V_{CC} = 5 V$ ;  $T_{amb} = 25 \circ C$ ; values are given for an IF amplifier with 500  $\Omega$  load (measured as shown in Figure 7 for the PAL standard); unless otherwise specified.

| Symbol                                                 | Parameter                        | Conditions                                                           | Min | Тур  | Max      | Unit |

|--------------------------------------------------------|----------------------------------|----------------------------------------------------------------------|-----|------|----------|------|

| Functional                                             | range                            |                                                                      |     |      |          |      |

| V <sub>POR</sub>                                       | power-on reset supply voltage    | for a voltage lower than V <sub>POR</sub> , power-on reset is active | 1.5 | 3.5  | -        | V    |

| Ν                                                      | divider ratio                    | 15-bit frequency word                                                | 64  | -    | 32767    |      |

| f <sub>XTAL</sub>                                      | crystal oscillator frequency     | $R_{XTAL}$ = 25 $\Omega$ to 300 $\Omega$                             | 3.2 | 4.0  | 4.48     | MHz  |

| Z <sub>XTAL</sub>                                      | input impedance (absolute value) | $f_{XTAL} = 4 \text{ MHz}$                                           | 600 | 1200 | -        | Ω    |

| PMOS ports                                             | s: P0, P1, P2 and P3             |                                                                      |     |      |          |      |

| I <sub>LO</sub>                                        | output leakage current           | $V_{CC} = 5.5 \text{ V}; V_{Pn} = 0 \text{ V}$                       | -   | -    | 10       | μA   |

| V <sub>DS(P0)(sat)</sub>                               | output saturation voltage        | buffer P0 is on only; sourcing 10 mA                                 | -   | 0.25 | 0.4      | V    |

| V <sub>DS(P1)(sat)</sub>                               | output saturation voltage        | buffer P1 is on only; sourcing 20 mA                                 | -   | 0.25 | 0.4      | V    |

| V <sub>DS(P2)(sat)</sub> ,<br>V <sub>DS(P3)(sat)</sub> | output saturation voltage        | buffer P2 or P3 is on; sourcing 5 mA                                 | -   | 0.25 | 0.4      | V    |

| NPN ports:                                             | P4 and P6                        |                                                                      |     |      |          |      |

| I <sub>LO</sub>                                        | output leakage current           | V <sub>CC</sub> = 5.5 V; V <sub>Pn</sub> = 6 V                       | -   | -    | 10       | μA   |

| V <sub>CE(sat)</sub>                                   | output saturation voltage        | buffer P4 or P6 is on; sinking 5 mA                                  | -   | 0.25 | 0.4      | V    |

| ADC input                                              |                                  |                                                                      |     |      |          |      |

| VI                                                     | ADC input voltage                | see Table 13                                                         | 0   | -    | $V_{CC}$ | V    |

| I <sub>IH</sub>                                        | HIGH-level input current         | ADC input $V_i = V_{CC}$                                             | -   | -    | 10       | μΑ   |

| IIL                                                    | LOW-level input current          | ADC input $V_i = 0 V$                                                | -10 | -    | -        | μΑ   |

| AS input (a                                            | ddress selection)                |                                                                      |     |      |          |      |

| I <sub>IH</sub>                                        | HIGH-level input current         | AS input $V_i = V_{CC}$                                              | -   | -    | 10       | μΑ   |

| IIL                                                    | LOW-level input current          | AS input $V_i = 0 V$                                                 | -10 | -    | -        | μΑ   |

| SCL and SE                                             | DA inputs                        |                                                                      |     |      |          |      |

| VIL                                                    | LOW-level input voltage          |                                                                      | 0   | -    | 1.5      | V    |

| V <sub>IH</sub>                                        | HIGH-level input voltage         |                                                                      | 2.3 | -    | 5.5      | V    |

| I <sub>IH</sub>                                        | HIGH-level input current         | $V_{BUS} = 5.5 \text{ V};  V_{CC} = 0 \text{ V}$                     | -   | -    | 10       | μΑ   |

|                                                        |                                  | $V_{BUS}$ = 5.5 V; $V_{CC}$ = 5.5 V                                  | -   | -    | 10       | μΑ   |

### 5 V mixer/oscillator and synthesizer for PAL and NTSC standards

#### Table 19: PLL ... continued

$V_{CC} = 5 V$ ;  $T_{amb} = 25 \circ C$ ; values are given for an IF amplifier with 500  $\Omega$  load (measured as shown in Figure 7 for the PAL standard); unless otherwise specified.

| Symbol               | Parameter                                    | Conditions                                                                                                   | Min | Тур | Max  | Unit |

|----------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| I <sub>IL</sub>      | LOW-level input current                      | $V_{BUS} = 1.5 \text{ V}; V_{CC} = 0 \text{ V}$                                                              | -   | -   | 10   | μA   |

|                      |                                              | $V_{BUS}$ = 0 V; $V_{CC}$ = 5.5 V                                                                            | -10 | -   | -    | μA   |

| SDA outpu            | it                                           |                                                                                                              |     |     |      |      |

| I <sub>LO</sub>      | leakage current                              | SDA output $V_o = 5.5 V$                                                                                     | -   | -   | 10   | μA   |

| Vo                   | output voltage                               | I <sub>o(sink)</sub> = 3 mA                                                                                  | -   | -   | 0.4  | V    |

| <b>Clock freq</b>    | uency                                        |                                                                                                              |     |     |      |      |

| f <sub>clk</sub>     | clock frequency                              |                                                                                                              | -   | -   | 400  | kHz  |

| Charge pu            | mp output CP                                 |                                                                                                              |     |     |      |      |

| I <sub>IH</sub>      | HIGH-level input current<br>(absolute value) | CP = 1                                                                                                       | -   | 280 | -    | μΑ   |

| I <sub>IL</sub>      | LOW-level input current (absolute value)     | CP = 0                                                                                                       | -   | 60  | -    | μΑ   |

| I <sub>LO(off)</sub> | off-state leakage current                    | T2 = 0; T1 = 1; T0 = 0                                                                                       | -15 | 0   | +15  | nA   |

| Tuning vol           | tage output VT                               |                                                                                                              |     |     |      |      |

| I <sub>LO(off)</sub> | off-state leakage current                    | OS = 1; V <sub>VT</sub> = 33 V                                                                               | -   | -   | 10   | μA   |

| Vo                   | output voltage when the loop is closed       | $\begin{split} &OS = 0;  T2 = 0;  T1 = 0;  T0 = 1; \\ &R_L = 27 \; k\Omega; \; V_{VT} = 33 \; V \end{split}$ | 0.2 | -   | 32.7 | V    |

#### Table 20: Mixer

$V_{CC} = 5 V$ ;  $T_{amb} = 25 \degree C$ ; values are given for an IF amplifier with 500  $\Omega$  load (measured as shown in Figure 7 for the PAL standard); unless otherwise specified.

| Symbol              | Parameter                            | Conditions                                                              |     | Min          | Тур               | Max              | Unit               |

|---------------------|--------------------------------------|-------------------------------------------------------------------------|-----|--------------|-------------------|------------------|--------------------|

| Low band            | mixer mode (P0 = 1 and P1 =          | • 0); including IF amplifier                                            |     |              |                   |                  |                    |

| f <sub>RF</sub>     | RF frequency                         | picture carrier                                                         | [1] | 44.25        | -                 | 154.25           | MHz                |

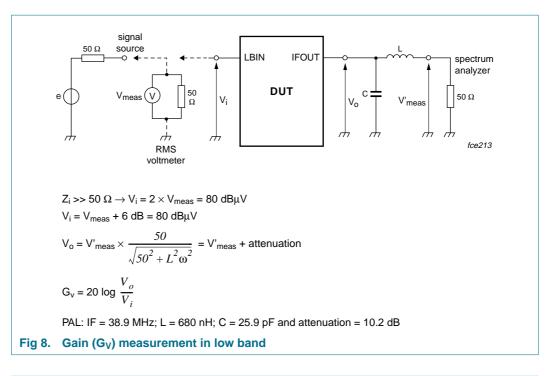

| Gv                  | voltage gain                         | f <sub>RF</sub> = 44.25 MHz; see <u>Figure 8</u>                        |     | 25.0         | 27.5              | 30               | dB                 |

|                     |                                      | f <sub>RF</sub> = 157 MHz; see <u>Figure 8</u>                          |     | 25.0         | 27.5              | 30               | dB                 |

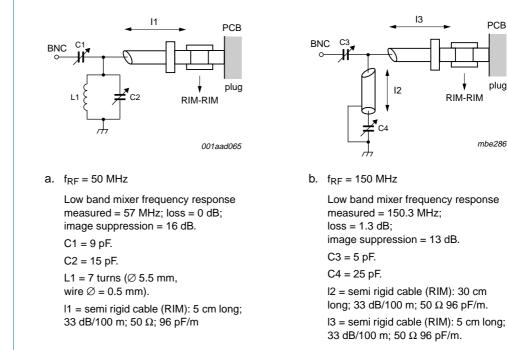

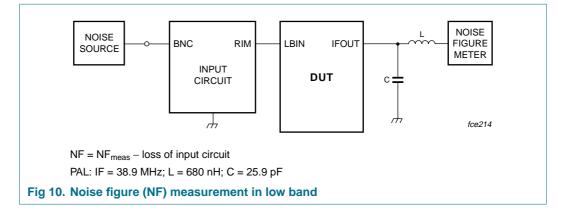

| NF                  | noise figure                         | $f_{RF} = 50 \text{ MHz}$ ; see Figure 9 and 10                         |     | -            | 8.0               | 10.0             | dB                 |

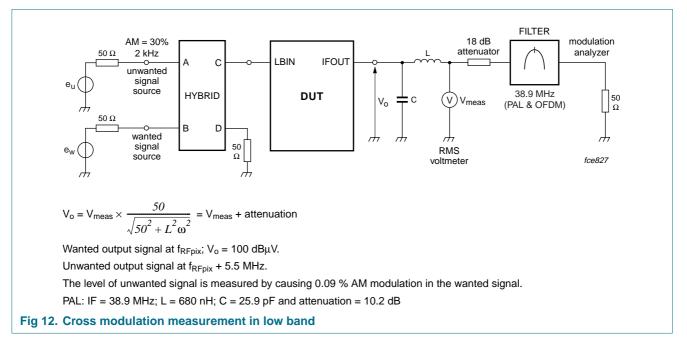

| V <sub>o(mod)</sub> | output voltage causing               | $f_{RF} = 44.25 \text{ MHz}; \text{ see } \frac{\text{Figure } 12}{12}$ |     | 108          | 111               | -                | dBµV               |

|                     | 0.3 % cross modulation in<br>channel | f <sub>RF</sub> = 157 MHz; see <u>Figure 12</u>                         |     | 108          | 111               | -                | dBμV               |

| V <sub>o(FM)</sub>  | output voltage causing               | f <sub>RF</sub> = 44.25 MHz                                             | [2] | 108          | 111               | -                | dBµV               |

|                     | 1.1 kHz incidental FM                | f <sub>RF</sub> = 157 MHz                                               | [2] | 108          | 111               | -                | dBµV               |

| INT <sub>SO2</sub>  | channel SO2 beat                     | $V_{RFpix} = 115 \text{ dB}\mu \text{V}$ at IF output                   | [3] | 57           | 60                | -                | dBc                |

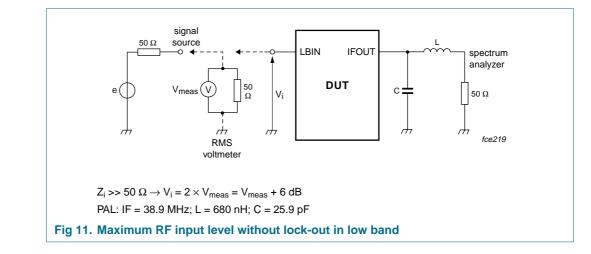

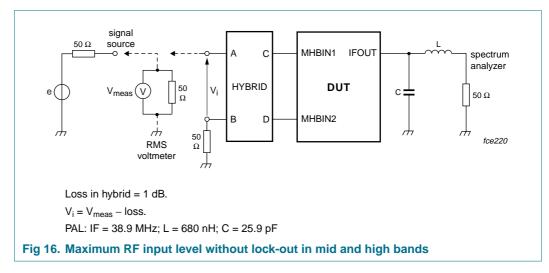

| Vi                  | input level without lock-out         | see Figure 11                                                           | [4] | -            | -                 | 120              | dBµV               |

| 9 <sub>os</sub>     | optimum source                       | f <sub>RF</sub> = 50 MHz                                                |     | -            | 0.7               | -                | mS                 |

|                     | conductance for noise figure         | f <sub>RF</sub> = 150 MHz                                               |     | -            | 0.9               | -                | mS                 |

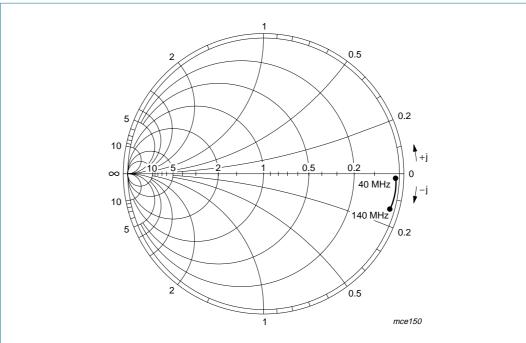

| 9i                  | input conductance                    | f <sub>RF</sub> = 44.25 MHz; see <u>Figure 4</u>                        |     | -            | 0.30              | -                | mS                 |

|                     |                                      | f <sub>RF</sub> = 161.25 MHz; see <u>Figure 4</u>                       |     | -            | 0.33              | -                | mS                 |

| C <sub>i</sub>      | input capacitance                    | f <sub>RF</sub> = 44.25 to 161.25 MHz;<br>see Figure 4                  |     | -            | 1.29              | -                | pF                 |

| High band           | d mixer in mid band mode (P0         | = 0 and P1 = 1); including IF amplifier                                 |     |              |                   |                  |                    |

| f <sub>RF</sub>     | RF frequency                         | picture carrier                                                         | [1] | 161.25       | -                 | 439.25           | MHz                |

| 397 750 15057       |                                      |                                                                         |     | © Koninklijk | e Philips Electro | onics N.V. 2005. | All rights reserve |

|                     |                                      | D 00 441 0005                                                           |     |              |                   |                  |                    |

### 5 V mixer/oscillator and synthesizer for PAL and NTSC standards

#### Table 20: Mixer ... continued

$V_{CC} = 5 V$ ;  $T_{amb} = 25 \circ C$ ; values are given for an IF amplifier with 500  $\Omega$  load (measured as shown in Figure 7 for the PAL standard); unless otherwise specified.

| Symbol                | Parameter                                                    | Conditions                                                                               |            | Min    | Тур | Max    | Unit |

|-----------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------|------------|--------|-----|--------|------|

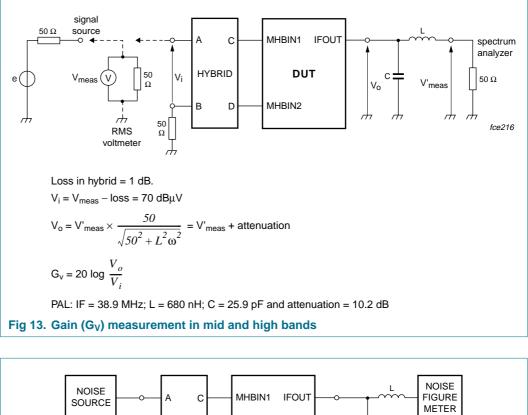

| Gv                    | voltage gain                                                 | f <sub>RF</sub> = 157 MHz; see <u>Figure 13</u>                                          |            | 35     | 38  | 41     | dB   |

|                       |                                                              | f <sub>RF</sub> = 443 MHz; see <u>Figure 13</u>                                          |            | 35     | 38  | 41     | dB   |

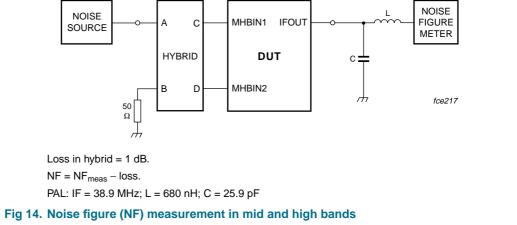

| NF                    | noise figure (not corrected                                  | f <sub>RF</sub> = 157 MHz; see <u>Figure 14</u>                                          |            | -      | 6   | 8.0    | dB   |

|                       | for image)                                                   | f <sub>RF</sub> = 443 MHz; see <u>Figure 14</u>                                          |            | -      | 6   | 8.0    | dB   |

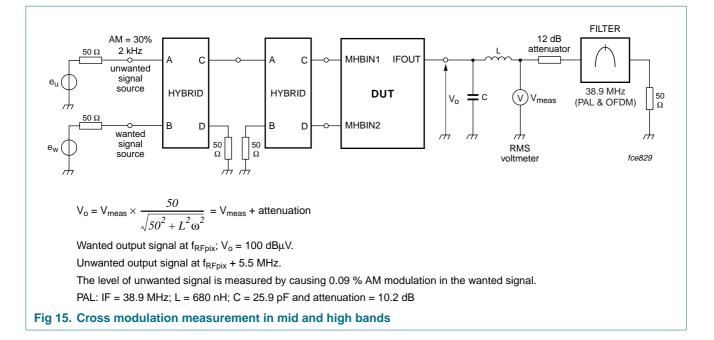

| V <sub>o(mod)</sub>   | output voltage causing                                       | f <sub>RF</sub> = 157 MHz; see <u>Figure 15</u>                                          |            | 108    | 111 | -      | dBμV |

|                       | 0.3 % cross modulation in<br>channel                         | f <sub>RF</sub> = 443 MHz; see <u>Figure 15</u>                                          |            | 108    | 111 | -      | dBμV |

| V <sub>o(FM)</sub>    | output voltage causing                                       | f <sub>RF</sub> = 157 MHz                                                                | [2]        | 108    | 111 | -      | dBμV |

|                       | 1.1 kHz incidental FM                                        | f <sub>RF</sub> = 443 MHz                                                                | [2]        | 108    | 111 |        | dBμV |

| V <sub>f(N+5)-1</sub> | (N + 5) – 1 MHz pulling                                      | $f_{RFwanted}$ = 443 MHz; $f_{osc}$ = 481.9 MHz;<br>$f_{RFunwanted}$ = 482 MHz           | [5]        | 72     | 80  | -      | dBμV |

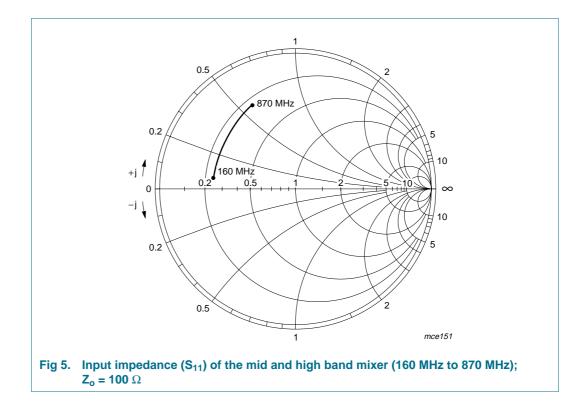

| Zi                    | input impedance (R <sub>S</sub> + jL <sub>S</sub> ω)         | $R_S$ at $f_{RF}$ = 157 MHz; see <u>Figure 5</u>                                         |            | -      | 25  | -      | Ω    |

|                       |                                                              | $R_S$ at $f_{RF}$ = 443 MHz; see Figure 5                                                |            | -      | 25  | -      | Ω    |

|                       |                                                              | $L_S$ at $f_{RF}$ = 157 MHz; see Figure 5                                                |            | -      | 13  | -      | nH   |

|                       |                                                              | $L_S$ at $f_{RF}$ = 443 MHz; see Figure 5                                                |            | -      | 13  | -      | nH   |

| Vi                    | input level without lock-out                                 | see Figure 16                                                                            | [4]        | -      | -   | 120    | dBµV |

| High band             | mixer in high band mode (P                                   | 0 = 0 and P1 = 0); including IF amplifier                                                | •          |        |     |        |      |

| f <sub>RF</sub>       | RF frequency                                                 | picture carrier                                                                          | [1]        | 455.25 | -   | 855.25 | MHz  |

| Gv                    | voltage gain                                                 | f <sub>RF</sub> = 443 MHz; see <u>Figure 13</u>                                          |            | 35     | 38  | 41     | dB   |

|                       |                                                              | f <sub>RF</sub> = 863.25 MHz; see <u>Figure 13</u>                                       |            | 35     | 38  | 41     | dB   |

| NF                    | noise figure (not corrected                                  | f <sub>RF</sub> = 443 MHz; see <u>Figure 14</u>                                          |            | -      | 6.0 | 8.0    | dB   |

|                       | for image)                                                   | f <sub>RF</sub> = 863.25 MHz; see <u>Figure 14</u>                                       |            | -      | 7.0 | 9.0    | dB   |

| V <sub>o(mod)</sub>   | output voltage causing                                       | f <sub>RF</sub> = 443 MHz; see <u>Figure 15</u>                                          |            | 108    | 111 | -      | dBμV |

|                       | 0.3 % cross modulation in<br>channel                         | $f_{RF} = 863.25 \text{ MHz}; \text{ see } \frac{\text{Figure } 15}{1000 \text{ MHz}}$   |            | 108    | 111 | -      | dBμV |

| V <sub>o(FM)</sub>    | output voltage causing                                       | f <sub>RF</sub> = 443 MHz                                                                | [2]        | 108    | 111 | -      | dBμV |

|                       | 1.1 kHz incidental FM                                        | f <sub>RF</sub> = 863.25 MHz                                                             | [2]        | 108    | 111 | -      | dBμV |

| V <sub>f(N+5)-1</sub> | (N + 5) – 1 MHz pulling                                      | $f_{RFwanted}$ = 863.25 MHz;<br>$f_{osc}$ = 902.15 MHz;<br>$f_{RFunwanted}$ = 902.25 MHz | <u>[5]</u> | 72     | 80  | -      | dBμV |

| Zi                    | input impedance (R <sub>S</sub> + jL <sub>S</sub> $\omega$ ) | $R_S$ at $f_{RF}$ = 443 MHz; see Figure 5                                                |            | -      | 25  | -      | Ω    |

|                       |                                                              | $R_S$ at $f_{RF}$ = 863.25 MHz; see Figure 5                                             |            | -      | 23  | -      | Ω    |

|                       |                                                              | $L_S$ at $f_{RF}$ = 443 MHz; see Figure 5                                                |            | -      | 13  | -      | nH   |

|                       |                                                              | $L_S$ at $f_{RF}$ = 863.25 MHz; see Figure 5                                             |            | -      | 13  | -      | nH   |

| Vi                    | input level without lock-out                                 | see Figure 16                                                                            | [4]        | -      | -   | 120    | dBµV |

[1] The RF frequency range is defined by the oscillator frequency range and the Intermediate Frequency (IF).

[2] This is the level of the RF unwanted signal, 50 % amplitude modulated with 1 kHz, that causes a 1.1 kHz FM modulation of the local oscillator and thus of the wanted signal; V<sub>wanted</sub> = 100 dBμV; f<sub>unwanted</sub> = f<sub>wanted</sub> + 5.5 MHz. The FM modulation is measured at the oscillator output with a peeking coil using a modulation analyzer with a peak-to-peak detector and a post detection filter of 300 Hz up to 3 kHz.

[3] Channel SO2 beat is the interfering product of  $f_{RFpix}$ ,  $f_{IF}$  and  $f_{osc}$  of channel SO2;  $f_{beat}$  = 37.35 MHz. The possible mechanisms are:  $f_{osc} - 2 \times f_{IF}$  or  $2 \times f_{RFpix} - f_{osc}$ . For the measurement  $V_{o(IFOUT)} = V_{RFpix}$  = 115 dBµV.

# **TDA6500; TDA6501**

#### 5 V mixer/oscillator and synthesizer for PAL and NTSC standards

- [4] The IF output signal stays stable within the range of the  $f_{ref}$  step for a low level RF input up to 120 dB $\mu$ V. This should be verified for every channel in the band.

- [5] (N + 5) 1 MHz pulling is the input level of channel N + 5, at frequency 1 MHz lower, causing FM sidebands 30 dB below the wanted carrier.

© Koninklijke Philips Electronics N.V. 2005. All rights reserved.

### 5 V mixer/oscillator and synthesizer for PAL and NTSC standards

#### Table 21: Oscillator

$V_{CC} = 5 V$ ;  $T_{amb} = 25 \degree C$ ; values are given for an IF amplifier with 500  $\Omega$  load (measured as shown in Figure 7 for the PAL standard); unless otherwise specified.

| Symbol                            | Parameter                                                        | Conditions                                                                                           | Min            | Тур    | Max    | Unit   |

|-----------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------|--------|--------|--------|

| Low band                          | oscillator                                                       |                                                                                                      |                |        |        |        |

| f <sub>osc</sub>                  | oscillator frequency                                             |                                                                                                      | <u>[1]</u> 84. | 15 -   | 193.15 | MHz    |

| $\Delta f_{osc(V)}$               | oscillator frequency shift with                                  | $\Delta V_{CC} = 5 \%$                                                                               | [2] _          | 20     | 70     | kHz    |

|                                   | supply voltage                                                   | $\Delta V_{CC} = 10 \%$                                                                              | [2] _          | 110    | -      | kHz    |

| $\Delta f_{\text{osc}(\text{T})}$ | oscillator frequency drift with temperature                      | $\Delta T = 25 \text{ °C}; V_{CC} = 5 \text{ V with}$ compensation                                   | <u>[3]</u> _   | 800    | 1100   | kHz    |

| $\Delta f_{osc(t)}$               | oscillator frequency switch-on drift                             | 5 s to 15 min after switching on $V_{CC}$ = 5 V                                                      | <u>[4]</u> _   | 500    | 700    | kHz    |

| $\Phi_{\sf osc}$                  | phase noise, carrier-to-noise<br>sideband                        | $\pm$ 10 kHz frequency offset; worst case in the frequency range                                     | 84             | 87     | -      | dBc/Hz |

|                                   |                                                                  | ±100 kHz frequency offset; worst case in the frequency range                                         | 104            | 107    | -      | dBc/Hz |

| RSC <sub>p-p</sub>                | ripple susceptibility of V <sub>CC</sub><br>(peak-to-peak value) | 4.75 V < V <sub>CC</sub> < 5.25 V; worst case<br>in the frequency range; ripple<br>frequency 500 kHz | <u>[5]</u> 15  | 20     | -      | mV     |

| Mid band                          | oscillator                                                       |                                                                                                      |                |        |        |        |

| f <sub>osc</sub>                  | oscillator frequency                                             |                                                                                                      | [1] 200        | 0.15 - | 478.15 | MHz    |

| $\Delta f_{osc(V)}$               | oscillator frequency shift with                                  | $\Delta V_{CC} = 5 \%$                                                                               | [2] _          | 20     | 70     | kHz    |

|                                   | supply voltage                                                   | $\Delta V_{CC} = 10 \%$                                                                              | [2] _          | 110    | -      | kHz    |

| $\Delta f_{osc(T)}$               | oscillator frequency drift with temperature                      | $\Delta T = 25 \text{ °C}; V_{CC} = 5 \text{ V with}$ compensation                                   | <u>[3]</u> _   | 1000   | 1500   | kHz    |

| $\Delta f_{\text{osc}(t)}$        | oscillator frequency drift after switch-on                       | 5 s to 15 min after switching on $V_{CC}$ = 5 V                                                      | <u>[4]</u> _   | 500    | 700    | kHz    |

| $\Phi_{\sf OSC}$                  | phase noise, carrier-to-noise<br>sideband                        | $\pm$ 10 kHz frequency offset; worst case in the frequency range                                     | 84             | 87     | -      | dBc/Hz |

|                                   |                                                                  | ±100 kHz frequency offset; worst case in the frequency range                                         | 104            | 107    | -      | dBc/Hz |

| RSC <sub>p-p</sub>                | ripple susceptibility of V <sub>CC</sub><br>(peak-to-peak value) | 4.75 V < V <sub>CC</sub> < 5.25 V; worst case<br>in the frequency range; ripple<br>frequency 500 kHz | <u>5</u> 15    | 20     | -      | mV     |

| High band                         | oscillator                                                       |                                                                                                      |                |        |        |        |

| f <sub>osc</sub>                  | oscillator frequency                                             |                                                                                                      | <u>[1]</u> 494 | .15 -  | 894.15 | MHz    |

| $\Delta f_{osc(V)}$               | oscillator frequency shift with                                  | $\Delta V_{CC} = 5 \%$                                                                               | [2] _          | 20     | 70     | kHz    |

|                                   | supply voltage                                                   | $\Delta V_{CC}$ = 10 %                                                                               | [2] _          | 300    | -      | kHz    |

| $\Delta f_{\text{osc}(\text{T})}$ | oscillator frequency drift with temperature                      | $\Delta T = 25 \text{ °C}; V_{CC} = 5 \text{ V}$ with compensation                                   | [3] _          | 1100   | 1500   | kHz    |

| $\Delta f_{\text{osc}(t)}$        | oscillator frequency drift after switch-on                       | 5 s to 15 min after switching on $V_{CC}$ = 5 V                                                      | <u>[4]</u> _   | 600    | 900    | kHz    |

#### 5 V mixer/oscillator and synthesizer for PAL and NTSC standards

#### Table 21: Oscillator ... continued

$V_{CC} = 5 V$ ;  $T_{amb} = 25 \circ C$ ; values are given for an IF amplifier with 500  $\Omega$  load (measured as shown in <u>Figure 7</u> for the PAL standard); unless otherwise specified.

| Symbol             | Parameter                                                        | Conditions                                                                                                            | Min                      | Тур | Max | Unit   |

|--------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------|-----|-----|--------|

| $\Phi_{\rm OSC}$   | phase noise, carrier-to-noise sideband                           | $\pm 10 \text{ kHz}$ frequency offset; worst case in the frequency range                                              | 84                       | 87  | -   | dBc/Hz |

|                    |                                                                  | ±100 kHz frequency offset; worst case in the frequency range                                                          | 104                      | 107 | -   | dBc/Hz |

| RSC <sub>p-p</sub> | ripple susceptibility of V <sub>CC</sub><br>(peak-to-peak value) | $4.75 \text{ V} < \text{V}_{CC} < 5.25 \text{ V}$ ; worst case<br>in the frequency range; ripple<br>frequency 500 kHz | <u><sup>[5]</sup></u> 15 | 20  | -   | mV     |

[1] Limits are related to the tank circuits used in Figure 7 for a PAL application. The choice of different external components adapts the measurement circuit to other frequency bands or NTSC applications.

[2] The frequency shift is defined as a change in oscillator frequency when the supply voltage varies from  $V_{CC} = 5 \text{ V}$  to 4.75 V (4.5 V) or from  $V_{CC} = 5 \text{ V}$  to 5.25 V (5.5 V). The oscillator is free running during this measurement.

- [3] The frequency drift is defined as a change in oscillator frequency when the ambient temperature varies from T<sub>amb</sub> = 25 °C to 50 °C or from T<sub>amb</sub> = 25 °C to 0 °C. The oscillator is free running during this measurement.

- [4] Switch-on drift is defined as the change in oscillator frequency between 5 s and 15 min after switch on. The oscillator is free running during this measurement.

- [5] The supply ripple susceptibility is measured in the circuit according to Figure 7 using a spectrum analyzer connected to the IF output. An unmodulated RF signal is applied to the test board RF input. A sinewave signal with a frequency of 500 kHz is superimposed onto the supply voltage. The amplitude of this ripple signal is adjusted to bring the 500 kHz sidebands around the IF carrier to a level of –53.5 dB with respect to the carrier.

#### Table 22: IF amplifier

$V_{CC} = 5 V$ ;  $T_{amb} = 25 \circ C$ ; values are given for an IF amplifier with 500  $\Omega$  load (measured as shown in Figure 7 for the PAL standard); unless otherwise specified.

| Symbol              | Parameter                                                     | Conditions                                             | Min           | Тур  | Max | Unit |

|---------------------|---------------------------------------------------------------|--------------------------------------------------------|---------------|------|-----|------|

| IF amplifie         | r                                                             |                                                        |               |      |     |      |

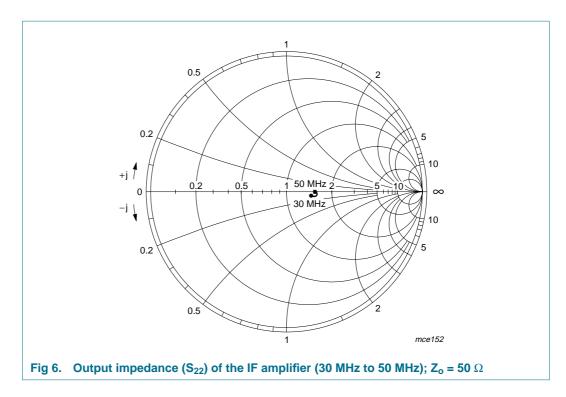

| S <sub>22</sub>     | output reflection coefficient                                 | magnitude; see Figure 6                                | -             | 38   | -   | dB   |

|                     |                                                               | phase; see Figure 6                                    | -             | 0.36 | -   | deg  |

| Zo                  | output impedance (R <sub>S</sub> + jL <sub>S</sub> $\omega$ ) | R <sub>S</sub> at 36.15 MHz                            | -             | 79   | -   | Ω    |

|                     |                                                               | C <sub>S</sub> at 36.15 MHz                            | -             | 9    | -   | nF   |

|                     |                                                               | R <sub>S</sub> at 43.5 MHz                             | -             | 80   | -   | Ω    |

|                     |                                                               | C <sub>S</sub> at 43.5 MHz                             | -             | 3    | -   | nF   |

| Rejection           | at the IF output                                              |                                                        |               |      |     |      |

| INT <sub>div</sub>  | level of divider interferences<br>in the IF signal            | worst case                                             | <u>[1]</u> _  | -    | 23  | dBμV |

| INT <sub>XTAL</sub> | crystal oscillator interferences rejection                    | $V_{IF}$ = 100 dBµV; worst case in the frequency range | 2 60          | 66   | -   | dBc  |

| INTf <sub>ref</sub> | reference frequency rejection                                 | $V_{IF}$ = 100 dBµV; worst case in the frequency range | <u>[3]</u> 60 | 66   | -   | dBc  |

[1] This is the level of divider interferences close to the IF. For example channel S3:  $f_{osc} = 158.15$  MHz,  $\frac{1}{4}f_{osc} = 39.5375$  MHz. The LOSCIN input must be left open (i.e. not connected to any load or cable); the HOSCIN1 and HOSCIN2 inputs are connected to a hybrid.

[2] Crystal oscillator interference means the 4 MHz sidebands caused by the crystal oscillator. The rejection has to be greater than 60 dB for an IF output signal of 100 dBμV.